### 特点

- ▶ 兼容 "ISO 11898-2:2016", "SAE J2284-1~ SAE J2284-5"和 "SAE J1939-14"标准

- ▶ 具有 CiA 601-4:2019 中定义的 CAN 信号改善功能

- ▶ 内置过温保护

- ▶ 总线端口±42V 耐压

- ▶ 驱动器 (TXD) 显性超时功能

- ▶ 带远程唤醒功能的低功耗待机模式

- ➤ SIT1462Q/3 I/O 电压范围支持 1.8V、3.3V 和 5V MCU

- ▶ VCC 和 VIO 电源引脚上具有欠压保护

- ➤ 高速 CAN, 支持 5Mbps 灵活数据速率 (CAN FD) (Flexible Data-Rate) 以及在点对点的网络中支持 8Mbps 灵活数据速率

- ▶ 高抗电磁干扰能力

- ▶ 未上电节点不干扰总线

- ▶ 支持 SOP8 和 DFN3\*3-8 封装, DFN3\*3-8 具有改进的自动光学检测(AOI)能力

描述

SIT1462Q 是一款应用于 CAN 协议控制器和物理总线之间的接口芯片,可应用于车载、工业控制等领域,支持 8Mbps 灵活数据速率(Flexible Data-Rate),具有在总线与 CAN 协议控制器之间进行差分信号传输的能力。

| 参数                  | 符号                  | 最小  | 最大  | 单位 |

|---------------------|---------------------|-----|-----|----|

| 供电电压                | VCC                 | 4.5 | 5.5 | V  |

| MCU 侧端口电压           | VIO                 | 1.7 | 5.5 | V  |

| CANH、CANL<br>输入输出电压 | $V_{can}$           | -42 | +42 | V  |

| 总线差分电压              | $V_{\mathrm{diff}}$ | 1.5 | 3.0 | V  |

| 环境温度                | $T_{amb}$           | -40 | 125 | °C |

| 储存温度                | $T_{stg}$           | -55 | 150 | °C |

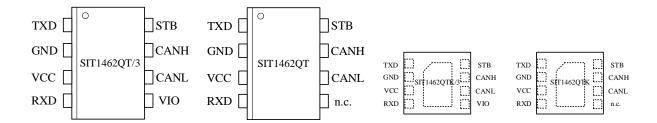

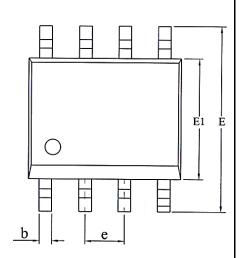

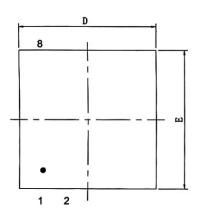

# 引脚分布图

# 引脚定义

| 引脚序号 | 引脚名称 | 引脚功能                         |  |

|------|------|------------------------------|--|

| 1    | TXD  | 发送器数据输入端                     |  |

| 2    | GND  | 地                            |  |

| 3    | VCC  | 5V 供电电源                      |  |

| 4    | RXD  | 接收器数据输出端                     |  |

| 5    | VIO  | 收发器 I/O 电平转换电源电压(SIT1462Q/3) |  |

| 5    | n.c. | 无连接(SIT1462Q)                |  |

| 6    | CANL | 低电位 CAN 总线输入输出端              |  |

| 7    | CANH | 高电位 CAN 总线输入输出端              |  |

| 8    | STB  | 高速与待机模式选择,低电平为高速             |  |

注: DFN3\*3-8 封装背面金属焊盘推荐接地。

## 极限参数

| 参数            | 符号                                                     | 测试条件                            | 大小        | 单位 |

|---------------|--------------------------------------------------------|---------------------------------|-----------|----|

| 电源电压          | V <sub>CC</sub> , V <sub>VIO</sub>                     | VCC,VIO 引脚                      | -0.3~+7   | V  |

| MCU 侧端口电<br>压 | V <sub>TXD</sub> , V <sub>RXD</sub> , V <sub>STB</sub> | TXD,RXD,STB 引脚                  | -0.3~+7   | V  |

| 总线侧输入电压       | V <sub>CANL</sub> , V <sub>CANH</sub>                  | CANH,CANL 引脚                    | -42~+42   | V  |

| 总线差分耐压        | V <sub>CANH-CANL</sub>                                 |                                 | -42~+42   | V  |

|               |                                                        | IEC 61000-4:2: CANH,<br>CANL 引脚 | -10~+10   | kV |

|               |                                                        | 人体模型(HBM),AEC Q1                | 00-002    |    |

|               |                                                        | 所有引脚                            | -4~+4     | kV |

| 静电放电电压        | $ m V_{ESD}$                                           | 对地,CANH和 CANL 引<br>脚            | -8~+8     | kV |

|               |                                                        | 充电模型 (CDM)                      |           |    |

|               |                                                        | 边角引脚                            | -750~+750 | V  |

|               |                                                        | 所有引脚                            | -500~+500 | V  |

|               |                                                        |                                 |           |    |

|               |                                                        | 脉冲                              | -100      | V  |

| 瞬态电压          | Vtrt                                                   | 脉冲 2a                           | 75        | V  |

|               |                                                        | 脉冲 3a                           | -150      | V  |

|               |                                                        | 脉冲 3b                           | 100       | V  |

| 存储温度范围        | $T_{\mathrm{stg}}$                                     |                                 | -55~150   | °C |

| 结温            | $T_{\rm j}$                                            |                                 | -40~150   | °C |

最大极限参数值是指超过这些值可能会使器件发生不可恢复的损坏。在这些条件之下是不利于 器件正常运作的,器件连续工作在最大允许额定值下可能影响器件可靠性,所有的电压的参考点为 地。

### 热阻特性

| 符号                | 参数                  | 测试条件     | 大小 | 单位   |

|-------------------|---------------------|----------|----|------|

| D                 | Junction-to-ambient | SOP8     | 95 | °C/W |

| $ m R_{	heta JA}$ | thermal resistance  | DFN3*3-8 | 65 | °C/W |

| D                 | Junction-to-case    | SOP8     | 46 | °C/W |

| $ m R_{	heta JC}$ | thermal resistance  | DFN3*3-8 | 35 | °C/W |

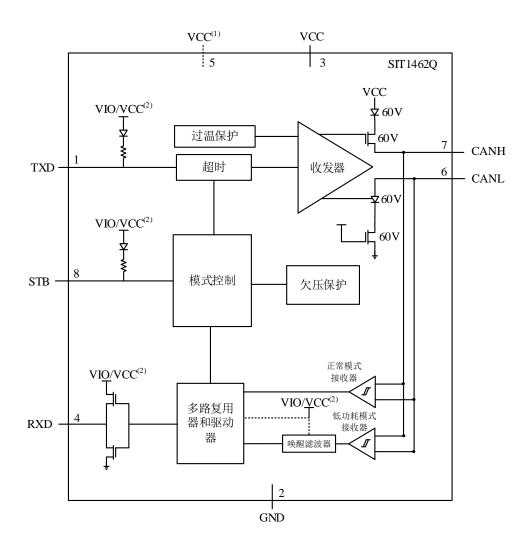

## 功能模块图

- (1) VIO 仅存在于 SIT1462Q/3 型号中, SIT1462Q 型号中 5 引脚无连接;

- (2) VIO 仅在 SIT1462Q/3 中, VCC 仅在 SIT1462Q 中。

直流参数

如无另外说明,在推荐的工作条件下进行测试:  $T_j$ =-40°C至 150°C, $V_{CC}$ =4.5V 至 5.5V、 $V_{IO}$ =1.7V 至 5.5V (SIT1462Q/3)、 $R_L$ =60 $\Omega$ 。

| 参数                | 符号                               | 测试条件                                                                                                | 最小                      | 典型  | 最大                      | 单位 |

|-------------------|----------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------|-----|-------------------------|----|

| 供电特性: VCC 端口      |                                  |                                                                                                     |                         |     |                         |    |

| 供电电压              | $V_{CC}$                         |                                                                                                     | 4.5                     | -   | 5.5                     | V  |

| 待机模式<br>欠压检测电压    | $V_{\mathrm{uvd}(\mathrm{stb})}$ |                                                                                                     | 3.4                     | -   | 4.5                     | V  |

| 待机模式<br>欠压迟滞电压    | $V_{uvhys(stb)}$                 |                                                                                                     | 50                      | -   | -                       | mV |

| 关断欠压检测电压          | $V_{uvd(swoff)} \\$              | SIT1462Q                                                                                            | 0.95                    | -   | 1.65                    | V  |

|                   |                                  | 正常模式;显性;<br>t <t<sub>to(dom)TXD; V<sub>TXD</sub>=0V</t<sub>                                         | -                       | 40  | 70                      | mA |

| VCC 供电电流          | I <sub>CC</sub>                  | 正常模式; 显性;<br>总线短路;<br>V <sub>TXD</sub> =0V;<br>-3V<(V <sub>CANH</sub> =V <sub>CANL</sub> )<br><+40V | -                       | -   | 125                     | mA |

|                   |                                  | 正常模式; 隐性;<br>V <sub>TXD</sub> =V <sub>IO</sub> <sup>(1)</sup>                                       | -                       | 4.2 | 10                      | mA |

|                   |                                  | 待机模式; SIT1462Q/3                                                                                    | -                       | -   | 2                       | μΑ |

|                   |                                  | 待机模式; SIT1462Q                                                                                      | -                       | -   | 21                      | μΑ |

| I/O 供电: VIO 端口    | (SIT1462Q/3)                     | )                                                                                                   |                         |     |                         |    |

| 供电电压              | $V_{IO}$                         |                                                                                                     | 1.7                     |     | 5.5                     | V  |

| 关断欠压检测电压          | $V_{uvd(swoff)}$                 |                                                                                                     | 0.95                    |     | 1.65                    | V  |

|                   |                                  | 正常模式;显性;<br>V <sub>TXD</sub> =0V                                                                    |                         | 240 | 760                     | μΑ |

| VIO 供电电流          | $I_{IO}$                         | 正常模式;隐性;<br>V <sub>TXD</sub> =V <sub>IO</sub> <sup>(1)</sup>                                        |                         | 120 | 460                     | μΑ |

|                   |                                  | 待机模式                                                                                                |                         |     | 21                      | μΑ |

| TXD 端口特性          |                                  |                                                                                                     |                         |     |                         |    |

| TXD 端口<br>高电平输入电压 | $ m V_{IH}$                      |                                                                                                     | 0.7 V <sub>IO</sub> (1) | -   | -                       | V  |

| TXD 端口<br>低电平输入电压 | $ m V_{IL}$                      |                                                                                                     | -                       | -   | 0.3 V <sub>IO</sub> (1) | V  |

| TXD 迟滞电压          | $V_{\text{hys}(TXD)}$            |                                                                                                     | 50                      | -   | -                       | mV |

| 上拉电阻              | $R_{pu}$                         |                                                                                                     | 20                      | -   | 80                      | kΩ |

| 输入电容              | $C_{i}$                          |                                                                                                     | -                       | -   | 10                      | pF |

| RXD端口特性           |                                  | •                                                                                                   | •                       |     | •                       |    |

| RXD 端口<br>高电平输出电流 | $I_{OH(RXD)}$                    | $V_{RXD}=V_{IO}-0.4V^{(1)}$                                                                         | -10                     | -   | -1                      | mA |

| 参数                | 符号                    | 测试条件                                                                                           | 最小                     | 典型   | 最大                     | 单位 |

|-------------------|-----------------------|------------------------------------------------------------------------------------------------|------------------------|------|------------------------|----|

| RXD 端口<br>低电平输出电流 | I <sub>OL(RXD)</sub>  | 总线显性;<br>V <sub>RXD</sub> =0.4V                                                                | 1                      | -    | 10                     | mA |

| STB 端口特性          |                       |                                                                                                |                        |      |                        |    |

| STB 端口<br>高电平输入电压 | $V_{\mathrm{IH}}$     |                                                                                                | 0.7V <sub>IO</sub> (1) | -    | -                      | V  |

| STB端口<br>低电平输入电压  | $V_{IL}$              |                                                                                                | -                      | -    | 0.3V <sub>IO</sub> (1) | V  |

| STB 迟滞电压          | $V_{\mathrm{hys}}$    |                                                                                                | 50                     | -    | -                      | mV |

| 上拉电阻              | $R_{pu}$              |                                                                                                | 20                     | -    | 80                     | kΩ |

| 输入电容              | $C_{i}$               |                                                                                                | -                      | -    | 10                     | pF |

| 过温保护              |                       |                                                                                                |                        |      |                        |    |

| 过温关断              | $T_{j(sd)}$           |                                                                                                | 165                    | -    | 185                    | °C |

| 释放过温关断            | $T_{j(sd)rel}$        |                                                                                                | 155                    | -    | 175                    | °C |

| 总线驱动器直流特性         |                       |                                                                                                | l L                    |      | L                      |    |

| CANH 输出电压<br>(显性) |                       | t <t<sub>to(dom)TXD; V<sub>TXD</sub>=0V;</t<sub>                                               | 2.89                   | 3.55 | 4.26                   | V  |

| CANL 输出电压<br>(显性) | $V_{O(dom)}$          | $R_L$ =50 $\Omega$ 至 65 $\Omega$                                                               | 0.77                   | 1.45 | 2.13                   | V  |

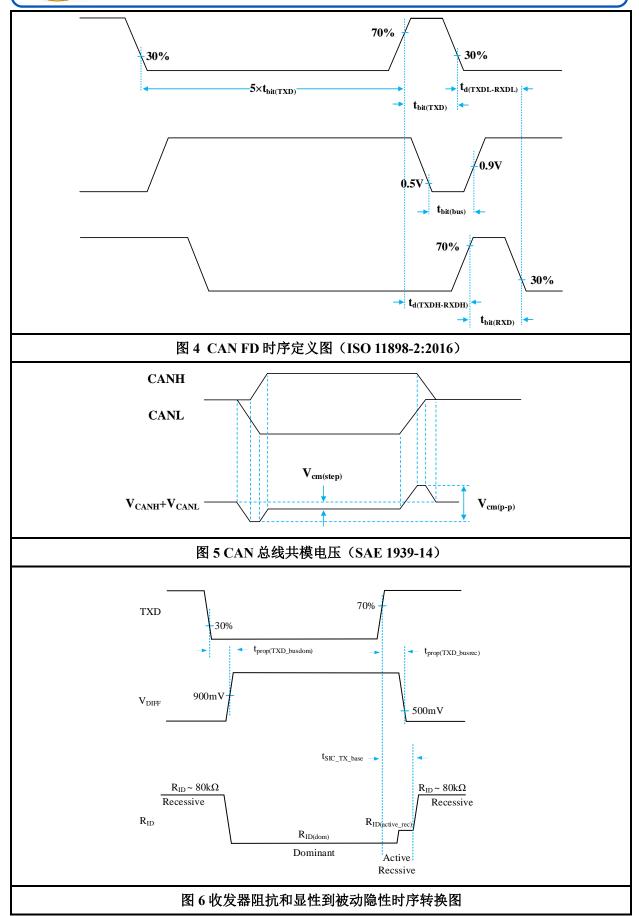

| 发送器电压对称性          | $V_{TXsym}$           | $V_{TXsym}=V_{CANH}+V_{CANL};$ $C_{SPLIT}=4.7nF;$ $f_{TXD}=250kHz$ , $1MHz$ 或 $2.5MHz$         | $0.9  m V_{CC}$        | -    | 1.1V <sub>CC</sub>     | V  |

| 共模电压              | $V_{\text{cm(step)}}$ |                                                                                                | -150                   | -    | 150                    | mV |

| 峰峰值共模电压           | V <sub>cm(p-p)</sub>  |                                                                                                | -300                   | -    | 300                    | mV |

|                   |                       | 正常模式; $t < t_{to(dom)TXD};$ $V_{TXD} = 0V;$ $V_{CC} = 4.5V 至 5.5V$ $R_L = 50\Omega 至 65\Omega$ | 1.5                    | -    | 3                      | V  |

| 总线输出差分电压<br>(显性)  | · 由 压                 | 正常模式; $t < t_{to(dom)TXD};$ $V_{TXD} = 0V;$ $V_{CC} = 4.5V 至 5.5V$ $R_L = 45\Omega 至 70\Omega$ | 1.4                    | -    | 3.3                    | V  |

|                   | $V_{O({ m diff})}$    | 正常模式;显性; $t < t_{to(dom)TXD};$ $V_{TXD} = 0V;$ $V_{CC} = 4.5V 至 5.5V$ $R_L = 2240\Omega$       | 1.5                    | -    | 5                      | V  |

|                   |                       | 正常模式;显性;<br>V <sub>TXD</sub> =V <sub>IO</sub> ; <sup>(1)</sup><br>无负载                          | -500                   | -    | +50                    | mV |

|                   |                       | 待机模式;显性;<br>无负载                                                                                | -0.2                   | -    | +0.2                   | V  |

| 参数                   | 符号                    | 测试条件                                                                                                                                     | 最小   | 典型  | 最大   | 单位 |

|----------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|----|

| 总线输出电压 (隐性)          | $V_{\mathrm{O(rec)}}$ | 正常模式;<br>V <sub>TXD</sub> =V <sub>IO</sub> ; <sup>(1)</sup><br>无负载                                                                       | 2    | 2.5 | 3    | V  |

| (100) [24.7          |                       | 待机模式;无负载                                                                                                                                 | -0.1 | -   | +0.1 | V  |

| 接收器差分阈值电压            | V                     | 正常模式;<br>-12V≤V <sub>CANH</sub> ≤12V<br>-12V≤V <sub>CANL</sub> ≤12V                                                                      | 0.5  | -   | 0.9  | V  |

| <b>按权</b> 益左为 國祖 电压  | $ m V_{th(RX)diff}$   | 待机模式;<br>-12V≤V <sub>CANH</sub> ≤12V<br>-12V≤V <sub>CANL</sub> ≤12V                                                                      | 0.4  | -   | 1.1  | V  |

| 接收器隐性电压区间            | $V_{\rm rec(RX)}$     | 正常模式;<br>-12V≤V <sub>CANH</sub> ≤12V<br>-12V≤V <sub>CANL</sub> ≤12V                                                                      | -4   | -   | 0.5  | V  |

| <b>以以祖</b> 修正宅丛区内    | v rec(RX)             | 待机模式;<br>-12V≤V <sub>CANH</sub> ≤12V<br>-12V≤V <sub>CANL</sub> ≤12V                                                                      | -4   | -   | 0.4  | V  |

| 接收器显性电压区间            | V                     | 正常模式;<br>-12V≤V <sub>CANH</sub> ≤12V<br>-12V≤V <sub>CANL</sub> ≤12V                                                                      | 0.9  | -   | 9    | V  |

| <b>按权益业</b> 压电压区间    | $V_{\text{dom(RX)}}$  | 待机模式;<br>-12V≤V <sub>CANH</sub> ≤12V<br>-12V≤V <sub>CANL</sub> ≤12V                                                                      | 1.1  | -   | 9    | V  |

| 接收器<br>差分电压迟滞区间      | $V_{hys(RX)dif} \\$   | 正常模式;<br>-12V≤V <sub>CANH</sub> ≤12V<br>-12V≤V <sub>CANL</sub> ≤12V                                                                      | 80   | -   | -    | mV |

| 短路输出电流               | $I_{O(SC)}$           | V <sub>CANH</sub> =-15V至40V;<br>V <sub>CANL</sub> =-15V至40V                                                                              |      | -   | 115  | mA |

| 隐性短路输出电流             | $I_{O(SC)\text{rec}}$ | V <sub>CANH</sub> =-27V至32V;<br>V <sub>CANL</sub> =-27V至32V;<br>V <sub>TXD</sub> =V <sub>IO</sub> 的时间<br>t>t <sub>d(TXD-busrec)end</sub> | -5   |     | 5    | mA |

| 总线漏电流                | $I_L$                 | $V_{CC}=V_{IO}=0V;$<br>或总线引脚通过 $47k\Omega$<br>短路到 $GND;$<br>$V_{CANH}=V_{CANL}=5V$                                                       | -10  |     | 10   | μΑ |

| CANH、CANL<br>输入电阻    | $R_{i}$               | -2V≤V <sub>CANH</sub> ≤7V<br>-2V≤V <sub>CANL</sub> ≤7V                                                                                   | 25   | 40  | 50   | kΩ |

| CANH、CANL<br>输入电阻失配度 | $\triangle R_i$       | 0V≤V <sub>CANH</sub> ≤5V<br>0V≤V <sub>CANL</sub> ≤5V                                                                                     | -2   |     | 2    | %  |

| CANH、CANL<br>差分输入电阻  | $R_{\text{ID}}$       | -2V≤V <sub>CANH</sub> ≤7V<br>-2V≤V <sub>CANL</sub> ≤7V                                                                                   | 50   | 80  | 100  | kΩ |

| CANH、CANL<br>共模输入电容  | $C_{i(cm)}^{{2}}$     |                                                                                                                                          | -    | -   | 40   | pF |

| CANH、CANL<br>差分输入电容  | $C_{i(diff)}$ (2)     |                                                                                                                                          | -    | -   | 20   | pF |

## 交流参数

如无另外说明,在推荐的工作条件下进行测试:  $T_j$ =-40°C至 150°C, $V_{CC}$ =4.5V 至 5.5V、 $V_{IO}$ =1.7V 至 5.5V (SIT1462Q/3)、 $R_L$ =60 $\Omega$ 。

| 参数                    | 符号                                 | 测试条件                                                                                                    | 最小             | 典型 | 最大  | 単位 |

|-----------------------|------------------------------------|---------------------------------------------------------------------------------------------------------|----------------|----|-----|----|

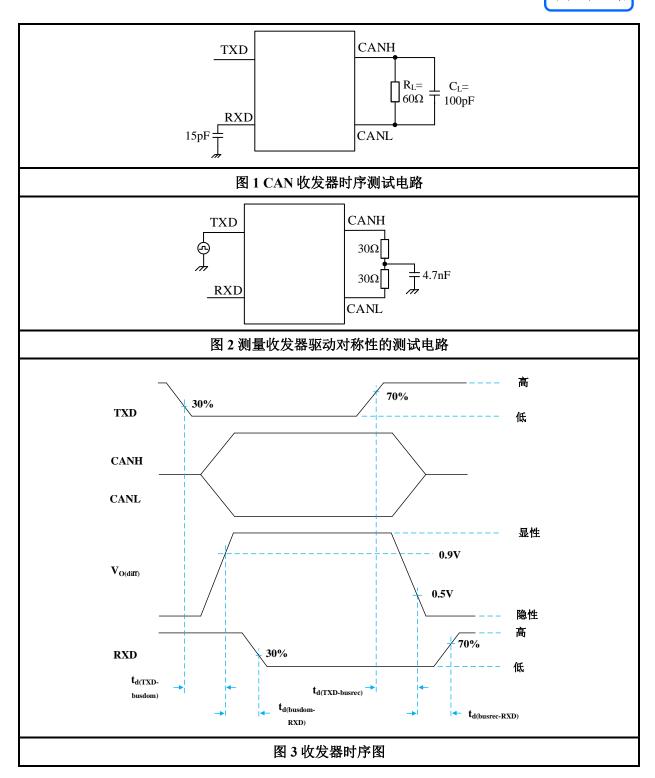

| CAN 时序特性; tbit        | (TXD)≥125ns;                       | 图 <u>1</u> 和 <u>图 3</u> 。                                                                               | •              |    |     |    |

| TXD 到总线显性的<br>延时时间    | $t_{d(TXD\text{-busdom})}$         | 正常模式                                                                                                    | -              | -  | 80  | ns |

| TXD 到总线隐性的<br>延时时间    | $t_{d(TXD\text{-busrec})}$         | 正常模式                                                                                                    | -              | -  | 80  | ns |

| 总线显性到 RXD 的<br>延时时间   | $t_{d(busdom-RXD)}$                | 正常模式                                                                                                    | -              | -  | 110 | ns |

| 总线隐性到 RXD 的<br>延时时间   | t <sub>d(busrec-RXD)</sub>         | 正常模式                                                                                                    | -              | -  | 110 | ns |

| TXD 低到 RXD 低<br>的延时时间 | $t_{d(TXDL\text{-}RXDL)}$          | 正常模式                                                                                                    | -              | -  | 190 | ns |

| TXD 高到 RXD 高<br>的延时时间 | t <sub>d(TXDH-RXDH)</sub>          | 正常模式                                                                                                    | -              | -  | 190 | ns |

| CAN FD 时序特性(          | CiA 601-4: 2                       | 2019); t <sub>bit(TXD)</sub> ≥125ns; <u>图 1</u> ₹                                                       | 和 <u>图 4</u> 。 |    |     |    |

| 信号改善时间                | t <sub>SIC_TXD_base</sub>          |                                                                                                         |                | -  | 530 | ns |

| 传输隐性位宽偏差              | $\Delta t_{bit(bus)}$ (2)          | $\Delta t_{bit(bus)} = t_{bit(bus)} - t_{bit(TXD)}$                                                     | -10            | -  | 10  | ns |

| 接收器时序对称性              | $\Delta t_{\rm rec}^{2}$           | $\Delta t_{rec} = t_{bit(RXD)} - t_{bit(bus)}$                                                          | -20            | -  | 15  | ns |

| 接收隐性位宽偏差              | $\Delta t_{bit(RXD)} \frac{(2)}{}$ | $\Delta t_{bit(RXD)} = t_{bit(RXD)} - t_{bit(TXD)}$                                                     | -30            | -  | 20  | ns |

| CAN FD 时序特性(          | (ISO 11898-2:                      | 2016); <u>图 1</u> 和 <u>图 4</u> 。                                                                        |                |    |     |    |

|                       |                                    | $\begin{array}{c} \text{2Mbit/s} \\ \text{(} t_{\text{bit(TXD)}} = 500 \text{ns}  \text{)} \end{array}$ | 480            | -  | 520 | ns |

| 传输隐性位宽                | $t_{ m bit(bus)}$                  | $\begin{array}{c} 5 \text{Mbit/s} \\ \text{($t_{bit(TXD)}$=} 200 \text{ns} ) \end{array}$               | 180            | -  | 220 | ns |

|                       |                                    | 8Mbit/s<br>(tbit(TXD)=125ns)                                                                            | 115            |    | 135 | ns |

|                       |                                    | 2Mbit/s                                                                                                 | -65            | -  | 40  | ns |

| 接收器时序对称性              | $\Delta t_{rec}$                   | 5Mbit/s                                                                                                 | -45            | -  | 15  | ns |

|                       |                                    | 8 Mbit/s                                                                                                | -20            |    | 15  | ns |

|                       |                                    | $\begin{array}{c} \text{2Mbit/s} \\ \text{(} t_{\text{bit(TXD)}} = 500 \text{ns}  \text{)} \end{array}$ | 470            | -  | 520 | ns |

| RXD 位时间               | $t_{\rm bit(RXD)}$                 | $5 \text{Mbit/s} $ $(t_{\text{bit(TXD)}} = 200 \text{ns})$                                              | 170            | -  | 220 | ns |

|                       |                                    | 8Mbit/s<br>(tbit(TXD)=125ns)                                                                            | 95             |    | 145 | ns |

| TXD 显性超时时间            | <del>,</del>                       |                                                                                                         |                |    |     |    |

| TXD 显性超时时间            | $t_{to(dom)TXD}$                   | VTXD=0V;正常模式                                                                                            | 0.8            | -  | 9   | ms |

| 参数            | 符号                        | 测试条件               | 最小  | 典型 | 最大  | 单位 |

|---------------|---------------------------|--------------------|-----|----|-----|----|

| 总线唤醒时间; CAN   | NH和 CANL                  | 引脚; <u>图 12</u> 。  | •   |    |     |    |

| 总线显性唤醒时间      | t <sub>wake(busdom)</sub> | 待机模式               | 0.5 | -  | 1.8 | μs |

| 总线隐性唤醒时间      | $t_{\text{wake(busrec)}}$ | 待机模式               | 0.5 | -  | 1.8 | μs |

| 总线唤醒超时时间      | $t_{to(wake)bus}$         | 待机模式               | 0.8 | -  | 9   | ms |

| 模式转换          |                           |                    |     |    |     |    |

| 模式转换时间        | $t_{t(moch)}$             |                    | -   | -  | 50  | μs |

| 开启时间          | $t_{\text{startup}}$      |                    | -   | -  | 1.5 | ms |

| RXD开启时间       | $t_{\text{startup}(RXD)}$ | 唤醒后切换到待机模式         | 4   | -  | 50  | μs |

| STB 引脚,IO 口滤泡 | 皮                         |                    |     |    |     |    |

| IO 口滤波时间      | $t_{\mathrm{filter(IO)}}$ |                    | 1   |    | 8   | μs |

| 欠压检测          |                           |                    |     |    |     |    |

| 欠压检测时间        | $t_{det(uv)}$             | VCC 引脚             | -   | -  | 50  | μs |

| 子账与工协测时间      | _                         | VCC 引脚; SIT1462Q   | -   | -  | 50  | μs |

| 关断欠压检测时间      | $t_{ m uvdt(swoff)}$      | VIO 引脚; SIT1462Q/3 | -   | -  | 50  | μs |

| 欠压恢复时间        | $t_{rec(uv)}$             | VCC 引脚             | -   | -  | 50  | μs |

- (1) V<sub>IO</sub>仅在 SIT1462Q/3 中。

- (2) 设计保证,非生产测试数据。

### 测试电路

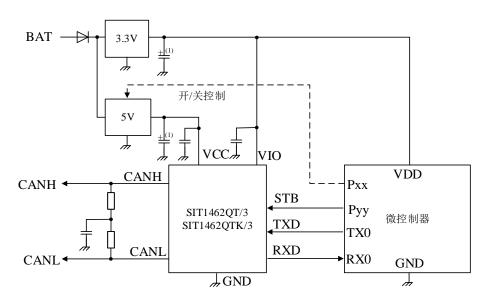

### 典型应用测试信息

(1) 根据电源调制器进行选用。

图 7 SIT1462Q/3 3.3V 微控制器典型应用

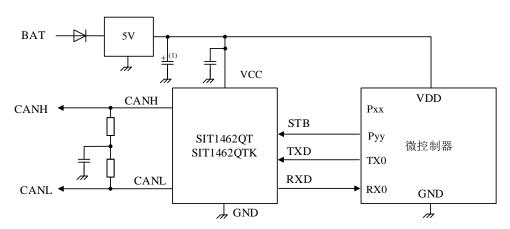

(1) 根据电源调制器进行选用。

图 8 SIT1462Q 5V 微控制器典型应用

说明

### 1 简述

SIT1462Q 是一款应用于 CAN 协议控制器和物理总线之间的接口芯片,可应用于车载、工业控制等领域,支持 8Mbps 灵活数据速率(Flexible Data-Rate),具有在总线与 CAN 协议控制器之间进行差分信号传输的能力。SIT1462Q 具有 CiA 601-4 中定义的 CAN 信号改善能力(SIC),可在更大的拓扑结构中进行可靠地 CAN FD 通讯。且 SIT1462Q 更严格的位时序对称性能,使其可在具有更高节点数和拓扑结构中进行 CAN FD 通信。

### 2 过温保护

SIT1462Q 具有过温保护功能,过温保护触发后,CAN 总线驱动器将禁用以保护设备免受过温环境损坏,因为驱动管是主要的耗能部件,关断驱动管可降低功耗从而降低芯片温度。当结温下降至  $T_{j(sd)rel}$ ,一旦 TXD 被重置为高,CAN 总线驱动器恢复至正常模式(等待 TXD 变为高,阻止输出驱动由于小的温度变化发生振荡)。

### 3 欠压保护

一旦 VCC 电压低于待机欠压检测阈值  $V_{uvd(stb)(VCC))}$ 的时间持续  $t_{det(uv)}$ ,收发器将切换至待机模式。VCC 恢复之前,STB 引脚的逻辑状态均被忽略。

在 SIT1462Q/3 中,一旦 VIO 电压低于关机欠压检测阈值  $V_{uvd(swoff)(VIO)}$ 的时间持续  $t_{uvd(swoff)}$ ,收发器将切换至关闭模式并与总线断开(高阻态),直到 VIO 恢复。

在 SIT1462Q 中,一旦 VCC 电压低于关机欠压检测阈值  $V_{uvd(swoff)(VCC)}$ 的时间持续  $t_{uvd(swoff)}$ ,收发器将切换至关闭模式并与总线断开(高阻态),直到 VCC 恢复。

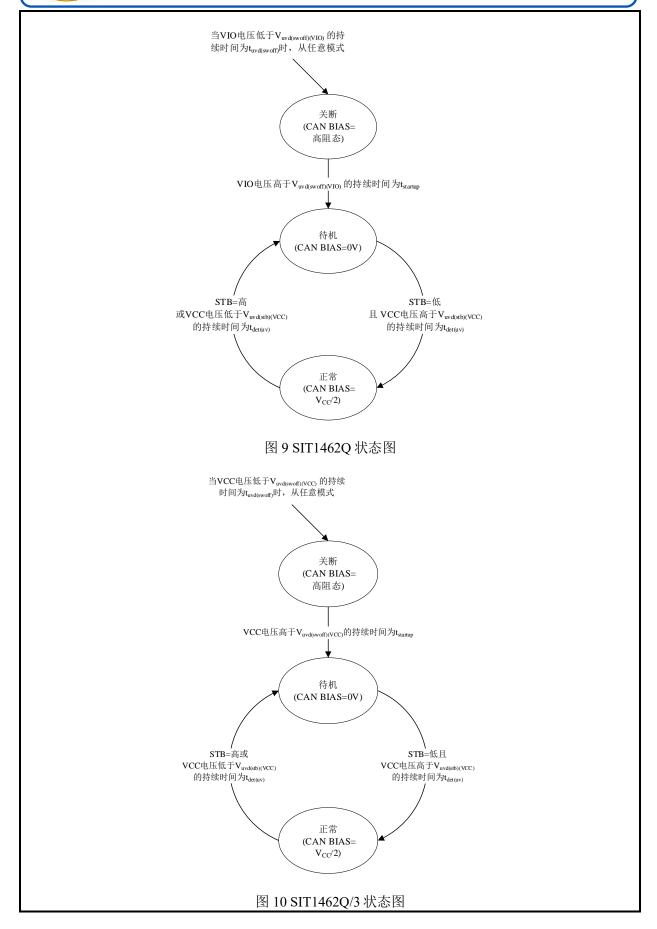

#### 4操作模式

SIT1462Q 支持三种工作模式: 正常、待机和关断模式,可通过引脚 STB 来选择。对应模式状态如表 1 所示。

| 模式                | 输入        |     | 输出           |            |         |

|-------------------|-----------|-----|--------------|------------|---------|

| 失八                | STB       | TXD | CAN驱动器       | RXD        |         |

|                   |           | 低   | 显性           | 低          |         |

| 正常                | 低         | 低高  | 占            | 隐性         | 总线显性时,低 |

|                   |           |     | 1 전 전        | 总线显性时,高    |         |

| 待机                | 高         | X   | 对地偏置         | 唤醒检测时,跟随总线 |         |

| 177/1             | 1寸7/1   同 |     | /1 / 四 / 画 . | 无唤醒检测时,高   |         |

| 关断 <sup>(1)</sup> | X         | X   | 高阻态          | 高阻态        |         |

(1) 当 VIO 或 VCC 引脚电压低于关断欠压检测阈值电压时,进入关断模式。

### 4.1 关断模式

当供电电压低于关断欠压阈值时,SIT1462Q 会从任意模式切换到关断模式。这为上电默认模

式。

在关断模式下, CAN 和 RXD 引脚处于高阻态。

### 4.2 待机模式

当供电电压高于关断欠压阈值时,SIT1462Q 开始启动,并触发初始程序。在 t<sub>startup</sub> 之后,切换至所选模式。

当引脚 STB 变为高电平时,选择待机模式。在此模式下,收发器无法发送或接收数据,并会激活一个低功耗接收器,以用来监视总线上的唤醒模式。发送器和正常模式接收器模块被关闭,总线引脚偏置到地,以将系统供电电流最小化。检测到唤醒请求后,RXD 引脚将跟随总线。

当 STB 强制为低时,会触发到正常模式的转换。

如果当 STB 为低时,供电电压低于待机模式欠压检测电压,SIT1462Q 将保持待机模式。待处理的唤醒事件将被清除,总线引脚上的差分数据通过低功耗接收器转换为数字数据并在 RXD 引脚上输出。在 SIT1462Q/3 中,低功耗接收器由 VIO 供电,并且当  $V_{IO}$ 高于关断欠压检测电压时(即使  $V_{IO}$ 是唯一可用的供电电压)也能检测到 CAN 总线活动。

#### 4.3 正常模式

当引脚 STB 为低电平时,选择正常模式,前提是 VCC 引脚上的供电电压高于待机欠压检测阈值 Vuvd(stb)。在此模式下,收发器可以通过总线线路 CANH 和 CANL 发送和接收数据。在正常模式开始传输之前,引脚 TXD 必须至少一次为高电平。差分接收器将总线线路上的模拟数据转换为数字数据,并通过引脚 RXD 输出。总线线路上输出信号的斜率由内部控制,并以优化的方式保证尽可能低的电磁辐射(EME)。为了支持高比特率,特别是在 CAN FD 系统中,信号改善功能在很大程度上消除了与拓扑相关的反射和阻抗不匹配。在隐性状态时,总线引脚上的输出电压为 VCC/2。

#### 4.4 操作模式和无间隙操作

无间隙操作保证了在所有电压水平下的确定性行为。供电电压到操作模式的映射详见<u>图 11</u> 以及状态图(图 9 和图 10)。

|        | 5.5V - 6V                 |         |               | 全功能                      |        |

|--------|---------------------------|---------|---------------|--------------------------|--------|

| VCC    | VCC 工作电压范<br>围(4.5V-5.5V) | 关断      | 全功能或关断        | 全功能并保证性<br>能             |        |

| VCC的电压 | VCC 待机模式下<br>欠压检测电压范<br>围 |         | 全功能或待机或<br>关断 | 全功能或待机                   | ,      |

|        | -0.3-4V                   |         | 待机或关断         | 待机                       |        |

|        |                           | -0.3-4V | -0.3-4V       | VIO工作电压范围<br>(2.95V-5.5V | 5.5-6V |

|        |                           |         | VIO电压         | 范围                       |        |

|               | 5.5V - 6V                 | 全功能          |

|---------------|---------------------------|--------------|

| ge on VCC     | VCC 工作电压范<br>围(4.5V-5.5V) | 全功能并保证性<br>能 |

| Voltage range | VCC 待机模式下<br>欠压检测电压范<br>围 | 全功能或待机       |

| Λo            | 2.95-4V                   | 待机           |

|               | VCC 关断欠压检测电压范围            | 待机或关断        |

|               | -0.3-2.65V                | 关断           |

图 11 供电电压范围和无间隙操作

#### 5 显性超时功能

当 TXD 引脚设置为低时,"TXD 显性超时"定时器启用。如果引脚 TXD 上的低电平持续时间超过内部定时器值 tto(dom)TXD,发送器将被禁用,驱动总线进入隐性状态。可防止引脚 TXD 因硬件或软件应用故障而被强制为永久低电平导致总线线路被驱动至永久显性状态(阻塞所有网络通信)。引脚 TXD 出现上升沿信号可复位。

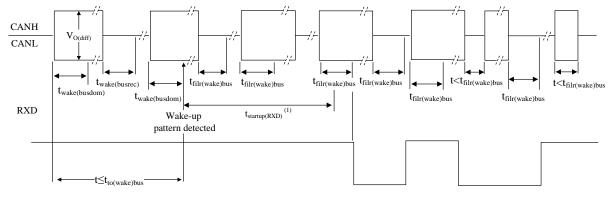

#### 6 远程唤醒功能

SIT1462Q 能被总线上专用唤醒帧从待机模式中唤醒。唤醒时序如图 12。

(1) 在 $t_{\text{startup(RXD)}}$ 期间,低功耗接收器开启,但RXD引脚不动作(即高电平或隐性)。在 $t_{\text{startup(RXD)}}$ 之后,结束的第一个宽度大于 $t_{\text{filr(wake)bus}}$ 的显性脉冲,将会触发RXD变为低电平或显性。

图 12 唤醒时序图

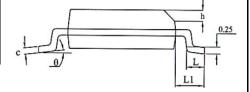

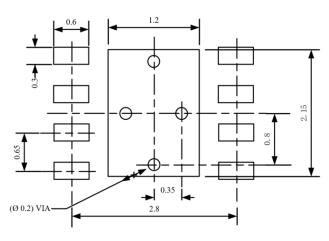

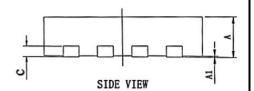

# SOP8 外形尺寸

### 封装尺寸

| 1  |        |         |        |  |  |

|----|--------|---------|--------|--|--|

| 符号 | 最小值/mm | 典型值/mm  | 最大值/mm |  |  |

| A  | -      | -       | 1.75   |  |  |

| A1 | 0.10   | -       | 0.225  |  |  |

| A2 | 1.30   | 1.40    | 1.50   |  |  |

| А3 | 0.60   | 0.65    | 0.70   |  |  |

| b  | 0.39   | -       | 0.47   |  |  |

| D  | 4.80   | 4.90    | 5.00   |  |  |

| Е  | 5.80   | 6.00    | 6.20   |  |  |

| E1 | 3.80   | 3.90    | 4.00   |  |  |

| e  |        | 1.27BSC |        |  |  |

| L  | 0.50   | -       | 0.80   |  |  |

| L1 |        | 1.05REF |        |  |  |

| С  | 0.20   |         | 0.24   |  |  |

| θ  | 0°     | -       | 8°     |  |  |

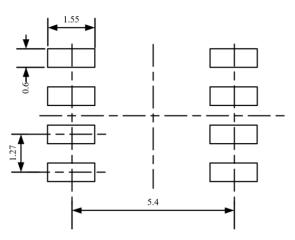

LAND PATTERN EXAMPLE (Unit: mm)

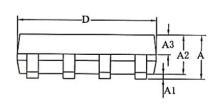

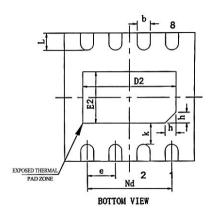

# DFN3\*3-8 外形尺寸

### 封装尺寸

| 符号 | 最小值/mm | 典型值/mm    | 最大值/mm |

|----|--------|-----------|--------|

| A  | 0.70   | 0.75      | 0.80   |

| A1 | 0      | 0.02      | 0.05   |

| A3 |        | 0.203 REF |        |

| D  | 2.90   | 3.00      | 3.10   |

| Е  | 2.90   | 3.00      | 3.10   |

| D2 | 2.05   | 2.15      | 2.25   |

| Nd |        | 1.95BSC   |        |

| E2 | 1.10   | 1.20      | 1.30   |

| b  | 0.25   | 0.30      | 0.35   |

| e  |        | 0.65BSC   |        |

| k  |        | 0.50REF   |        |

| L  | 0.35   | 0.40 0.43 |        |

| h  | 0.20   | 0.25      | 0.30   |

LAND PATTERN EXAMPLE (Unit: mm)

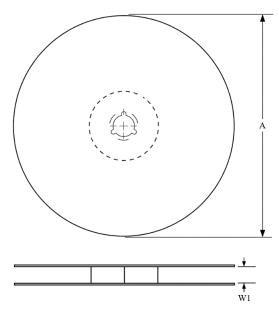

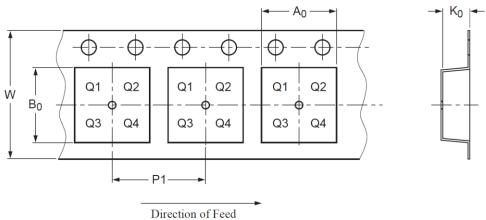

# 编带信息

| A0 | Dimension designed to accommodate the   |

|----|-----------------------------------------|

| AU | component width                         |

| В0 | Dimension designed to accommodate the   |

| DU | component length                        |

| K0 | Dimension designed to accommodate the   |

| ΚU | component thickness                     |

| W  | Overall width of the carrier tape       |

| P1 | Pitch between successive cavity centers |

PIN1 is in quadrant 1

| 封装类型     | 卷盘直径<br>A (mm) | 编带宽度<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) |

|----------|----------------|-----------------|------------|------------|------------|------------|-----------|

| SOP8     | 330±1          | 12.4            | 6.60±0.1   | 5.30±0.10  | 1.90±0.1   | 8.00±0.1   | 12.00±0.1 |

| DFN3*3-8 | 329±1          | 12.4            | 3.30±0.1   | 3.30±0.1   | 1.10±0.1   | 8.00±0.1   | 12.00±0.3 |

# 订购信息

| 定购代码         | 封装                 | 包装方式 |

|--------------|--------------------|------|

| SIT1462QT/3  | SOP8               | 盘装编带 |

| SIT1462QT    | SOP8               | 盘装编带 |

| SIT1462QTK/3 | DFN3*3-8, 小外形, 无引脚 | 盘装编带 |

| SIT1462QTK   | DFN3*3-8, 小外形, 无引脚 | 盘装编带 |

SOP8 编带式包装为 2500 颗/盘, DFN3\*3-8 编带式包装为 6000 颗/盘。

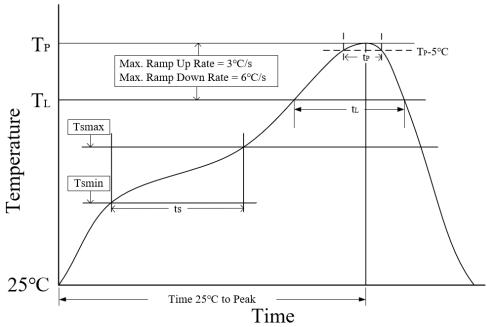

## 回流焊

| 参数                                                              | 无铅焊接条件          |

|-----------------------------------------------------------------|-----------------|

| 平均温升速率(T <sub>L</sub> to T <sub>P</sub> )                       | 3 °C/second max |

| 预热时间 ts(T <sub>smin</sub> =150 °C to T <sub>smax</sub> =200 °C) | 60-120 seconds  |

| 融锡时间 t <sub>L</sub> (T <sub>L</sub> =217 ℃)                     | 60-150 seconds  |

| 峰值温度 TP                                                         | 260-265 °C      |

| 小于峰值温度 5 ℃以内时间 tp                                               | 30 seconds      |

| 平均降温速率(T <sub>P</sub> to T <sub>L</sub> )                       | 6 °C/second max |

| 常温 25℃ 到峰值温度 Tp 时间                                              | 8 minutes max   |

### 重要声明

芯力特有权在不事先通知的情况下,保留更改上述资料的权利。

# 修订历史

| 版本号  | 修订内容                                                                                                 | 修订时间    |

|------|------------------------------------------------------------------------------------------------------|---------|

| V1.0 | 初始版本。                                                                                                | 2024.09 |

| V1.1 | 更新总线差分耐压 $V_{CANH\text{-}CANL}$ ;<br>更新总线侧输入电压 $V_{CANH}$ , $V_{CANH}$ ;<br>更新输入电阻失配度 $\Delta R_i$ 。 | 2024.10 |